## Zu DT-Übung 12.1

(Lösungsvorschlag)

## Zu 12.1a

Zur Frequenzteilung N:1 lassen sich unter anderem asynchrone Modulo-N-Dualzähler einsetzen, wenn man das Ausgangssignal des FlipFlops für die höchstwertigste Binärstelle verwendet. Dabei sind zwei Varianten möglich geeignet:

- als Modulo-N-Zähler mit direkt wirkenden Rücksetzeingängen, siehe Skript Kapitel 10.1.1.2.

- als Modulo-N-Zähler mit direkt wirkenden Setzeingängen, siehe Skript Kapitel 10.2.3.3.

In beiden Fällen muss man dafür sorgen, dass nach Erreichen des Zählerstandes N-1 beim folgenden Taktimpuls N alle FlipFlops unverzögert auf "0" gesetzt werden. Für Variante 1 werden dazu die Rücksetzeingänge aller FFs beschaltet, in Variante 2 nur diejenigen, deren zugeordnete Binärstellen sich nach dem Taktimpuls N-1 noch im Zustand "0" befinden. Der Grund liegt bei Variante 2 darin, dass der Modulo N-Zähler wieder bei 0 beginnen würde, wenn alle Stellen auf "1" liegen. Wenn man also die noch im "0"-Zustand befindlichen FFs vorzeitig auf "1" setzt, hat man diesen Fall erzwungen. Der Vorteil besteht u. a. darin, dass bei der bautechnischen Ausführung elektrische Verbindungen eingespart werden können.

Zum Entwurf ist für beide Varianten zunächst die Bestimmung der erforderlichen Anzahl m von FFs nötig. Es gilt die Regel:

$$2^m \ge N$$

oder  $m \ge \log_2 N$  mit der Nebenbedingung  $\rightarrow$  m ganzzahlig.

Man kann auch die beiden benachbarten Zweierpotenzen suchen, zwischen denen N liegt und m der höheren zuordnen. Im vorliegenden Fall ist N = 20. Dieser Wert liegt zwischen

$$2^4=16$$

und  $2^5=32$ , daher benötigt man m=5 FFs.

Diese FFs sind vom taktzustandsgesteuerten JK-MS-Typ und müssen mit direkt wirkenden Setz- bzw. Rücksetz-Eingängen ausgestattet sein.

In beiden Varianten wird die Rücksetzbedingung aus dem Zählerstand

$$N-1 = 19_{10} = 10011_2$$

abgeleitet. Ordnet man den FFs und den durch sie dargestellten Wertigkeiten die Bezeichnungen

$$\mathsf{E} \rightarrow (2^{16}),\, \mathsf{D} \rightarrow (2^8),\, \mathsf{C} \rightarrow (2^4),\, \mathsf{B} \rightarrow (2^2),\, \mathsf{A} \rightarrow (2^0)$$

zu, so gilt für die Rücksetzbedingung, dass

- E=1, B=1, A=1 ist

- und der nächste Taktimpuls T=20 die durch UND-Verknüpfung EBA entstehende "1" unmittelbar auf die Setz- bzw. Rücksetzeingänge durchschalten muss.

Bei invertierenden Setz- bzw. Rücksetzeingängen ist die "1" noch in eine "0" zu wandeln. Verwendet man diese FF-Ausführungen, so kann man ein NAND-Gatter mit 4 Eingängen vorsehen:

$$R = \overline{EBAT}$$

bzw.  $S = \overline{EBAT}$ .

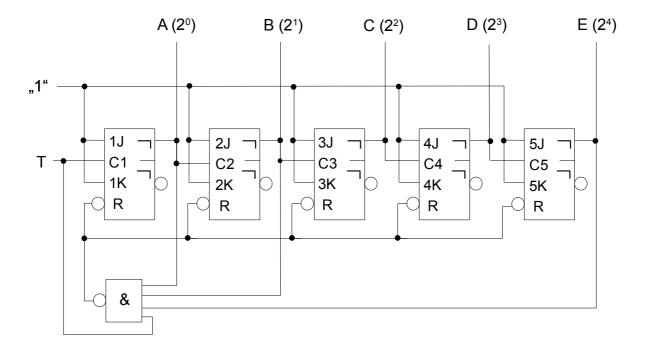

Damit erhält man für die Variante 1 (alle Rücksetzeingänge beschaltet) folgende Schaltung:

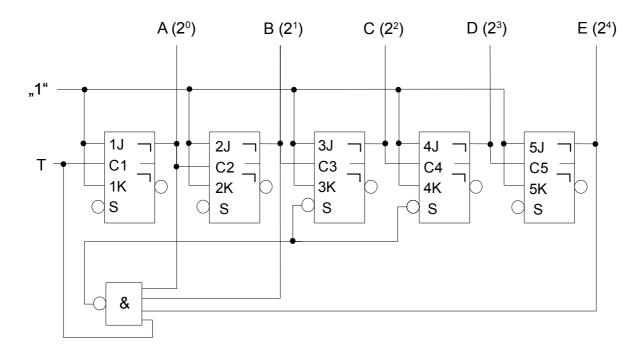

Bei der Variante 2 (Setzeingänge von C und D beschaltet) ergibt sich diese Schaltung:

**Zusatzaufgabe:** Überprüfen Sie, dass der Rücksetz- bzw. Setzvorgang tatsächlich so abläuft, wie vorgegeben, indem Sie z. B. für beide Varianten jeweils das Impulsdiagramm aller Signale für den Takt 19 und 20 skizzieren.

Frage: Sind taktflankengesteuerte FFs auch geeignet?

## Zu 12.1b:

Ein anderer Weg für Frequenzteilung N:1 ist die Reihenschaltung einzelner Teiler mit gegebenem Teilerverhältnis  $N_k$ , k= 1, 2, 3 ..., p. Dabei wird der erste Teiler mit den Impulsen der zu teilenden Frequenz  $f_E$  gespeist. Er liefert am Ausgang eine im Verhältnis  $N_1$ :1 geringere Frequenz und taktet damit den Teiler Nr. 2 usw. Am Ausgang des letzten Teilers Nr. p liegt dann eine Impulsfolge mit der Frequenz

$$f_A = \frac{f_N}{N_1 \cdot N_2 \cdot \dots \cdot N_p}$$

vor. Das gewünschte Teilerverhältnis N:1 erhält man demnach, wenn man die Einzelteilerverhältnisse so wählt, dass ihr Produkt gerade N ergibt.

Im vorliegenden Fall gibt es dazu 3 Möglichkeiten:

**Fall 1:** 20=10.2

Dafür ist die Reihenschaltung eines 10:1- und eines 2:1-Teilers geeignet. Beispiel:

- asynchroner 10:1 Teiler gemäß Skript, Kapitel 10.1.1.1

- T-FF für 2.1-Teilung, siehe Skript, Kapitel 9.2.1.4.3

**Fall 2:** 20=5.4

Reihenschaltung eines 5:1- und eines 4:1-Teilers. Beispiel:

Teilsynchroner Teiler 5:1 gemäß Beispiel im Skript, Kapitel 10.2.3.2. Dieser Teiler entsteht seinerseits durch Einbettung eines asynchronen 2:1-Teilers in einen synchronen 3:1 nach der Formel

$(2 \cdot k + 1)$ : 1 mit k = 2 für den asynchronen Teiler für k:1 in der Mitte.

Modulo 4-Zähler als synchroner 4:1-Teiler gemäß Skript, Kapitel 10.1.2

**Fall 3:** 20=5.2.2

Reihenschaltung eines 5:1- und zweier 2:1-Teiler. Beispiel:

- wie bei Fall 2: Teilsynchroner Teiler 5:1

- 2 T-FFs für je 2:1-Teilung

**Zusatzaufgabe:** Geben Sie für jeden der 3 Fälle wenigstens eine andere technische Realisierung an.